## A Single Phase High Frequency Link Inverter For Induction Motor Drive

# Prachi Lingarwar<sup>1</sup>, R.G.Shriwastava<sup>2</sup>, K.N.Sawalakhe<sup>3</sup>

<sup>1</sup> M.Tech. Research Scholar, PEPS, SDCOE, Wardha(M.S.),India <sup>2</sup> Associate Prof &Head. Elect. Deptt. BDCOE, Sewagram(M.S.),India <sup>3</sup> Assistant Prof &Head. Elect. Deptt. SDCOE, Wardha(M.S.),India

**Abstract:** This paper propose the analysis and design of a high-performance high frequency-link (HFL) single-phase inverter for single phase Induction motor drives. It offers bidirectional two-stage galvanic isolation power conversion without bulky dc link capacitors. An active clamper circuit and corresponding modulation strategy can be developed to enable this HFL converter to operate in soft-switching modes and be free of voltage spikes during device commutation. Power efficiency can be improved by reducing switching power losses. A high performance control schemes can also developed to enable it to equally function as a high-performance conventional pulse width modulation (PWM) inverter. This HFL inverter provides a high-reliability, high-efficiency, high-power-density, and high-performance power conversion solution.

**Keywords:** frequency, Induction motor, modulation, switching.

#### 1. Introduction

The growing requirement for high power density, compact size, and reduced weight, without compromising efficiency, cost, and reliability, stimulates the development of high frequency- link (HFL) power converters .Due to increasing concerns about global warming and potential energy crisis, renewable energy generation has drawn many attentions in last decade. To make use of the naturally fluctuating renewable energy, power converters have become the necessary part of a renewable energy generation system. For renewable energy generation system including different energy sources (solar, wind, and tidal energy), it is common to use a bidirectional converter. The use of new efficient photovoltaic array (PVA) has emerged as an alternative measure of renewable green power, energy conservation and demand-side management. PV arrays are built up with combined series/parallel combinations of PV solar. Compared to conventional pulse width modulation (PWM) converters with heavy and bulky line-frequency transformer, high-frequency (HF) transformer enables HFL power converters to offer high power density, compact size, and light weight . High frequency link power converters are receiving increasing attention as an alternative to more conversion power conversion system. Use of high frequency ac link in a power conversion system permits adjustment of the link voltage to meet the individual needs of loads/source in the system. By operating the link at high frequency, the system can be made compact because of the large reduction in the size and the weight of the transformer and passive components needed for filtering and temporary energy storage function. High frequency operation also speeds up the system response and if the frequency is above the audible range reduces acoustic noise.

High frequency link conversion has been employed very successfully in power converters. Their enormous success has demonstrated the benefits to some extent the difficulties of working at high frequencies. In particular, problems arise due to limitations of both the components and the circuit topologies as the demand has grown and technology has matured there has been a large improvement in the quality of components. High quality capacitors good magnetic materials for the design of compact low loss inductor and transformers and the semiconductor devices designed especially for high speed power applications have become available. This trend can be expected to continue in future with further improvement in performance and even with a large gains in the cost and availability of these components.

#### 2. Literature Review

This paper presents an evaluation of an isolated bi-directional DC-DC converter composed of a bi-directional boost chopper circuit and full-bridge-type LLC converter. In this paper, the confirmation of circuits operation, waveforms, measurement of conversion efficiency, and loss analysis for an isolated bi-directional DC-DC converter are carried out. From this work, it is clear that the loss of an isolated bi-directional DC-DC converter is

dependent on the switching time. Furthermore, it is confirmed that the conversion efficiency changes when the switching timing which affects ZVS level changes [1].

A new frequency converter which uses only three pairs of back to back thyristors and is capable of converting a three-phase fixed power frequency source to a single phase higher frequency has been introduced. Two equivalent circuit each viewed from power source and load have been derived. Their applicability's have been verified by comparing characteristic obtained from Simulation of the original circuits. By using those, it has been shown that the proposed converter has good characteristics in input power factor, input harmonics, and varied load condition is presented in [2].

This paper proposed a zero voltage switching (ZVS) technique for bidirectional dc/dc converters. The dc/dc unit considered had a two distinct bidirectional dc/dc cells paralleled at both input and output and whose two input bridges are coupled by means of passive inductive branches. A multiangle phase-shift modulation method is proposed which simultaneously achieves bidirectional power control, power sharing, and ZVS of all the electronic devices over the full power range without the need for auxiliary switches [3].

In this paper, a photovoltaic array (PVA) simulation model is used in Matlab-Simulink GUI environment is developed and presented. The model is developed using basic circuit equations of the photovoltaic (PV) solar cells including the effects of solar irradiation and temperature changes. The new model was tested using a directly coupled dc load as well as ac load via an inverter. Test and validation studies with proper load matching circuits are simulated [4].

This paper present a high-performance high frequency-link (HFL) single-phase inverter. It offers bidirectional two stage galvanic isolation power conversion without bulky dc link capacitors. An active clamper circuit and corresponding modulation strategy is developed to enable the proposed HFL rectifier to operate in soft-switching modes and be free of voltage spikes during device commutation. A succinct circuit model and high performance plug-in repetitive control scheme are also developed to enable it to equally function as a high performance conventional pulse width modulation (PWM) inverter. The proposed HFL inverter offers a high reliability, high-efficiency, high-power-density, and high-performance power conversion solution to extensive applications [5].

In this paper, a high-efficiency dc-dc converter with fast dynamic response for low-voltage photovoltaic (PV) sources is presented. The voltage stress of power switches is reduced at low-voltage side. Zero-current turn-off of output diodes is achieved at high-voltage side. Power efficiency is improved by reducing switching power losses. A modified proportional and integral controller is also suggested to achieve fast output voltage control. The dynamic response of the proposed converter is improved. [6]

## 3. Methodology

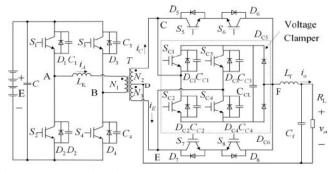

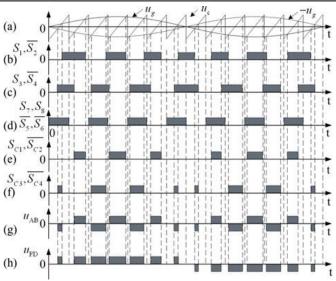

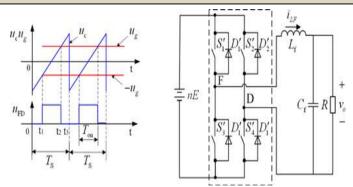

Fig. 1 shows the proposed HFL inverter, which mainly consists of high-frequency galvanic transformer T with turn ratio n, primary-side H-bridge converter (S1–S4), and secondary side ac/ac converter (S5–S8). It employs the switching strategy shown in Fig. 2, where ug and uc denote modulation signal and carrier signal, respectively. From Fig. 2, it can be seen that the modulation signal ug is actually converted into a typical unipolar PWM signal uFD, that is to say, the proposed HFL inverter can be treated as a typical unipolar PWM inverter. As shown in Fig.3, dead time is inserted between the PWM signals for the same bridge-leg switches i.e., S1 and S2, S3 and S4) of the secondary-side H-bridge converter in practical applications.

Fig. 1 High Frequency Link Single Phase Inverter with voltage Clamper circuit

Fig. 2 Modulation process of the proposed HFL PWM inverter with voltage clamper

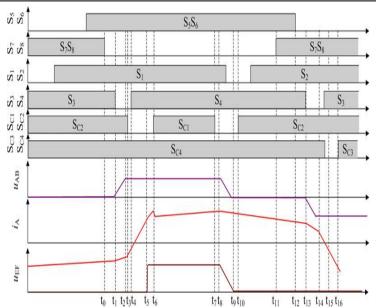

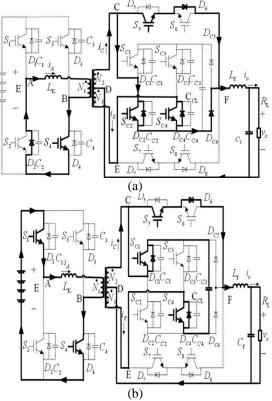

However, severe voltage spikes still occur during the H-bridge converter's commutation time due to the interruption of continuous current through the primary-side leakage inductance Lk of HF transformer T , which may damage power switches and cause output voltage distortion. As shown in Figs.1and 2, the active voltage clamper circuit and corresponding switching strategy is applied to remove voltage spikes and enable the inverter to operate in soft-switching modes. Fig.3 shows one typical operation scenario for the proposed clamper circuit in the case of ug> 0. The active voltage clamper circuit would operate in the following two modes: Clamping mode: As shown in Fig. 4(a), when both SC2 (DC2) and SC4 (DC4) are on, the secondary-side output voltage Uce will be clamped to zero, e.g., during the intervals of t0–t3 and t10–t13 shown in Fig.3; as shown in Fig. 4(b), when SC1 (DC1) and SC4 (DC4) are on, the secondary-side output voltage uCE will be clamped to 2nE, e.g., during the intervals of t3–t5 shown in Fig.3.

Transition mode: The time intervals between aforesaid two clamping modes are transition modes. As shown Fig.3, during the interval of t3–t5 , switch SC2 is turned OFF before the time instant of t5 ; during the intervals of t5–t6 and t7–t9 , switch SC1 is turned ON at t6 and turn OFF at t8 . ZVS commutation of the cycloconverter can be achieved during "zero-voltage" clamping mode of the clamper circuit; ZVS operation of primary-side dc/ac converter is almost the same as that of a full-bridge phase-shifted resonant PWM converter. However, as shown in Fig. 2, unlike typical fixed duty-cycle phase-shift PWM signals, the duty cycle of PWM signals for switches S1–S4 varies with the alternating modulation signal ug , the PWM signals for switches S3 and S4 will lead those for switches S1 and S2 when ug> 0, and the PWM signals for switches S1 and S2 will lead those for switches S1 and S2 when ug< 0. Such a phase-shift PWM control method enables all switches S1–S4 to evenly bear electrical stress and operate in soft-switching mode. Moreover, leakage inductance current varies with the alternating modulating signal ug . In the case of zero or small inductance current, it is impossible to achieve ZVS for both leading leg and lagging leg devices. It should be pointed out that there is duty cycle loss for the aforesaid modulation strategy

$$D_{LOSS} = \frac{t_{1-5}}{T_S} = L_K (I_1 + I_{Lf5}/n) / T_S E$$

Where  $I_1 = i_A(t_1)$ ,  $I_{Lf5} = i_{Lf}(t_5)$ , Since  $I_{Lf5}$  is an alternating,  $D_{LOSS}$  is not constant. The output root-mean-square voltage of the HFL inverter  $V_{out}$  is ,

$$V_{out} = nE(D - D_{LOSS})/\sqrt{2}$$

Fig.3 One typical operation scenario for the proposed clamper circuit when ug> 0

Corresponding to the modulation waveforms shown in Fig. 4.3, the switching states of all power switches during different time intervals are listed in Table I.

Fig.4 Clamping modes of the clamper circuit

- (a) Output of transformer clamped to  $\boldsymbol{0}$

- (b) Output of transformer clamped to 2nE

Fig. 5 Equivalent circuit of the proposed HFL inverter

Table I: Summary of the conducting components of the proposed HFL inverter at different intervals

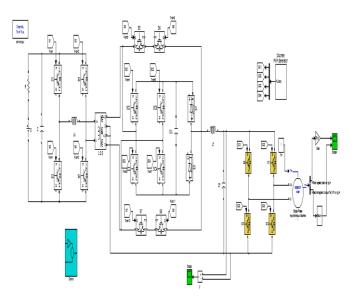

Fig.6 Simulated model of the single phase HFL inverter with capacitor start induction motor.

Fig. 7 Controlling circuit

| r                                |                               | T = -                                               |

|----------------------------------|-------------------------------|-----------------------------------------------------|

| Interval                         | Conducting components of      | Conducting                                          |

|                                  | the primary side              | components of                                       |

|                                  |                               | the secondary                                       |

|                                  |                               | side                                                |

| t <sub>0</sub> -t <sub>1</sub>   | $D_1,S_3$                     | $S_5, D_6, S_{C2},$                                 |

|                                  |                               | $S_{C4}$ , $D_{C6}$                                 |

| t <sub>1</sub> -t <sub>2</sub>   | D <sub>1</sub>                | S <sub>5</sub> , D <sub>6</sub> , S <sub>C2</sub> , |

|                                  |                               | $S_{C4}$ , $D_{C6}$                                 |

| t <sub>2</sub> -t <sub>3</sub>   | $D_1$ , $D_4$                 | $S_5, D_6, S_{C2},$                                 |

| 2 3                              | 17 4                          | $S_{C4}$ , $D_{C6}$                                 |

| t <sub>3</sub> -t <sub>4</sub>   | $D_1, D_4$                    | $S_5$ , $D_6$ , $D_{C2}$ ,                          |

| -5 -4                            | - 17 - 4                      | $S_{C4}$ , $D_{C6}$                                 |

| t <sub>4</sub> -t <sub>5</sub>   | $D_1 D_4$                     | $S_5, D_6, D_{C2},$                                 |

| 4 5                              |                               | $S_{C4}$ , $D_{C6}$                                 |

| t <sub>5</sub> -t <sub>6</sub>   | S <sub>1</sub> S <sub>4</sub> | $S_5, D_6$                                          |

| 15 16                            | 51 54                         | $S_5, D_6$                                          |

| t <sub>6</sub> -t <sub>7</sub>   | S <sub>1</sub> S <sub>4</sub> | $S_5, D_6,$                                         |

| -0 -7                            | -14                           | $S_{C1}(D_{C1}),$                                   |

|                                  |                               | $SC_4(D_{C4})$                                      |

| t <sub>7</sub> -t <sub>8</sub>   | $S_1 S_4$                     | $S_5, D_6$                                          |

| 1 68                             |                               | 55, 26                                              |

| t <sub>8</sub> -t <sub>9</sub>   | $S_4$                         | S <sub>5</sub> , D <sub>6</sub>                     |

|                                  | ·                             | J. U                                                |

| t <sub>9</sub> -t <sub>10</sub>  | $D_2 S_4$                     | $S_5, D_6$                                          |

|                                  |                               |                                                     |

| t <sub>10</sub> -t <sub>11</sub> | $D_2 S_4$                     | $S_5, D_6,$                                         |

|                                  |                               | $S_{C1}(D_{C1}),$                                   |

|                                  |                               | $SC_4(D_{C4})$                                      |

| t <sub>11</sub> -t <sub>12</sub> | $D_2 S_4$                     | $S_5, D_6,$                                         |

|                                  |                               | $S_{C1}(D_{C1}),$                                   |

|                                  |                               | $SC_4(D_{C4})$                                      |

| t <sub>12</sub> -t <sub>13</sub> | $D_2 S_4$                     | $S_7, D_8,$                                         |

|                                  |                               | $S_{C1}(D_{C1}),$                                   |

|                                  |                               | $SC_4(D_{C4})$                                      |

| t <sub>13</sub> -t <sub>14</sub> | $D_2$                         | S <sub>7</sub> , D <sub>8</sub> ,                   |

|                                  |                               | $S_{C1}(D_{C1}),$                                   |

|                                  |                               | $SC_4(D_{C4})$                                      |

|                                  | •                             |                                                     |

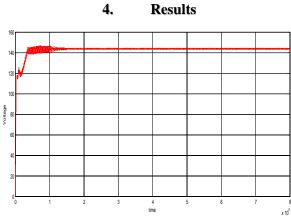

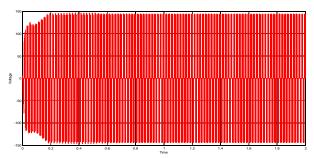

Fig. 8 Voltage waveform of the dc link with switching frequency 20 KHZ

Fig. 9 Voltage of the intermediate dc link with switching 50 KHZ frequency

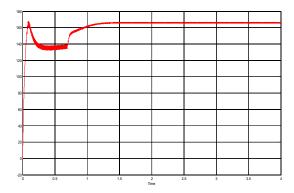

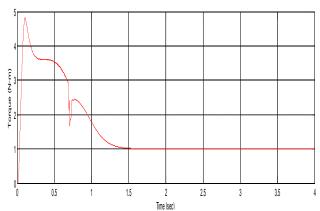

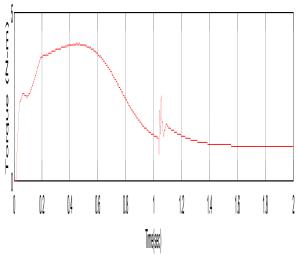

Fig.10 Torque of the capacitor start I.M with Switching frequency 20 KHZ

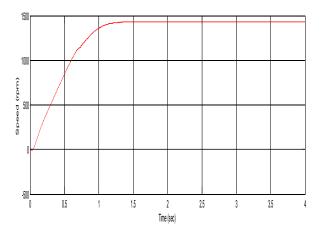

Fig.11 Speed of the capacitor start I.M with switching frequency 20 KHZ

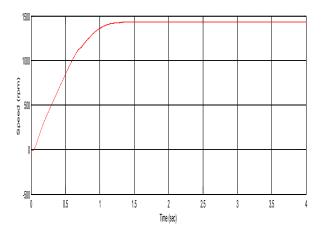

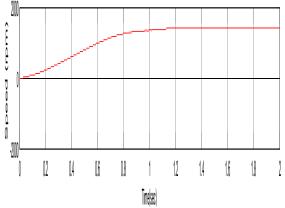

Fig.12 Speed of the capacitor start I.M with switching frequency 50 KHZ

Fig.13Torque of the capacitor start I.M with switching frequency 50 KHZ

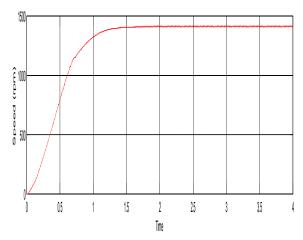

Fig. 14 Speed of the capacitor run I.M with switching frequency 20KHZ

Fig.15 Speed of the capacitor run I.M with switching frequency20KHZ

Fig.16 Ac output generated by the H-Bridge

Fig.17 Output of the transformer clamped to 2nE Inverter at the motor side

### 5. Conclusion

The proposed HFL inverter takes superior advantages over conventional HFL inverter and conventional PWM inverter: 1) soft-switching operation, high efficiency; 2) complete elimination of voltage spikes during commutation ensures safe operation of HF switching devices; 3) it can equally function as a conventional PWM inverter: easy for modeling and high-performance control. The clamper circuit provides the adjustment in the magnitude of the intermediate dc link. The performance characteristics of speed and torque of the Induction motor has been simulated at two different switching frequencies i.e 20 KHZ and 50 KHZ. The performance of induction motor has compared at both the switching frequencies. From the simulated result it has been found that motor works smoothly on switching frequency 20KHZ. On 50 KHZ, motor torque varies rapidly and the intermediate dc link voltage too. Motor can reached to its rated speed when operating at a switching frequency of 20 KHZ instead of 50 KHZ. For high frequency link operation, capacitor start induction motor work efficiently as compared to capacitor start capacitor run induction motor.

#### Referances

- [1]. Shinichiro Nagai., "Characteristic Evaluation for Bi-directional DC-DC Converter with Soft Switching", *IEEE Trans. Power Electronics, Volume: 28*, *Issue: 1, Jan 2013*

- [2]. Shin Okada , Teruo Tanaka , Hiroshi Kasahara., "A New High Frequency Cycloconverter", *Power Electronics, IEEE Trans.Vol. PE-1, NO. 4, October 1986.*

- [3]. Hyun-Lark do., "A Soft-Switching DC/DC Converter With High Voltage Gain", *Power Electronics, IEEE Trans.Vol. 25, No. 5, May 2010.*

- [4]. I.H.Atlas, A.M.Sharaf, "A Photovoltaic Array Simulation model For Matlab-Simulink GUI Environment",

- [5]. Wenjie Zhu, Keliang Zhou, Ming Cheng, "A Bidirectional High-Frequency-Link Single- phase Inverter: Modulation, Modeling, and Control", *IEEE Trans. Power electronics, Vol. 29, No. 8, August 2014.*

- [6]. Woo-Young Choi, "High-Efficiency DC–DC Converter With Fast Dynamic Response for Low-Voltage Photovoltaic Sources", *IEEE Trans. Power electronics*, Vol. 28, Issue:2,Feb.2013.

- [7]. Hsiu-Hao Liang, et.al., "Analysis and Implementation of a Bidirectional Double-Boost DC-DC Converter", *IEEE Trans. Power electronics, Vol.* 27, *Issue:* 4, *April* 2013.

- [8]. Shih-Ming Chen, et.al., "A Safety Enhanced, High Step-Up DC–DC Converter for AC Photovoltaic Module Application", *IEEE Trans. Power electronics, Vol. 27, No. 4, April 2012.*

- [9]. I. Yamato, N. Tokunaga, Y. Matsuda, H. Amano, and Y. Suzuki, "New conversion system for UPS using high frequency link," in Proc. IEEE Conf. Rec. 19th Annu. Power Electron. Spec., 1988, pp. 658–663.

- [10]. I. Yamato, N. Tokunaga, Y. Matsuda, H. Amano, and Y. Suzuki, "High frequency link DC-AC converter for UPS with a new voltage clamper," in Proc. IEEE 21st Annu. Power Electron. Spec. Conf., 1990, pp. 749–756.

- [11]. D. De and R. Venkataramanan, "Analysis, design, modeling, and implementation of an active clamp HF link converter," *IEEE Trans. Circuits Syst. I, vol. 58, no. 6, pp. 1146–1155, Jun. 2011.*